8对1多工器verilog 182354-8对1多工器verilog

基本的8對1多工器,使用Verilog與megafunction實現。 Introduction 使用環境:Quartus II 72 SP3 ModelSimAltera 61g DE2(Cyclone II EP2C35F672C6) Method 1: 自己撰寫Verilog mux_5_8_1v2v / Verilog 使用continuos assignment 本代码仅供学习参考 实验要求 8位并行乘法器 主要功能要求: 按键1,异步复位 按键2,流水灯,6个数码管显示学号后六位 按键3,调节8位乘法器的输入x,x显示到左边前2个数码管 按键4,调节8位乘法器的输入y,y显示到中间2个数码管 按键5,求值,按下后,计算x乘以y的结果,用z表示,并显示到 基于Verilog_HDL设计的出租车计价器doc,华北水利水电大学EDA课程设计 题 目: 出租车计价器 专 业: 通 信 工 程 年 级: 11级 学 生: 李高飞 学 号: 指导教师: 司孝平 完成日期: 13 年 12月 27日 摘 要:本文介绍了一种采用进行出租车计费器的设计本设计实现了出租车计费器所需的一些

Ppt 數位邏輯 使用verilog 設計powerpoint Presentation Free Download Id

8对1多工器verilog

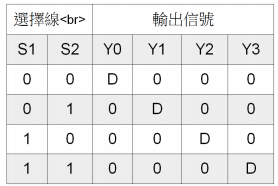

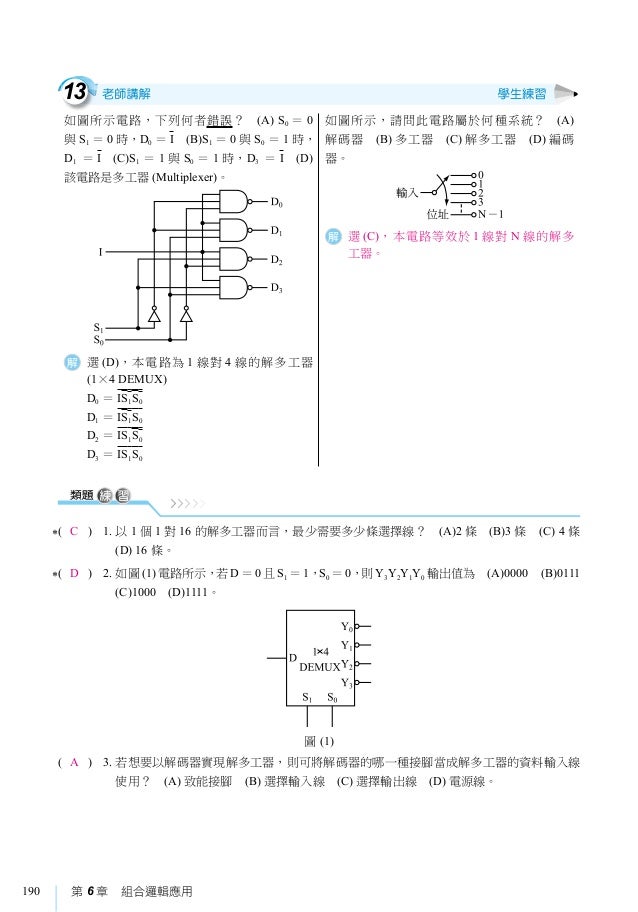

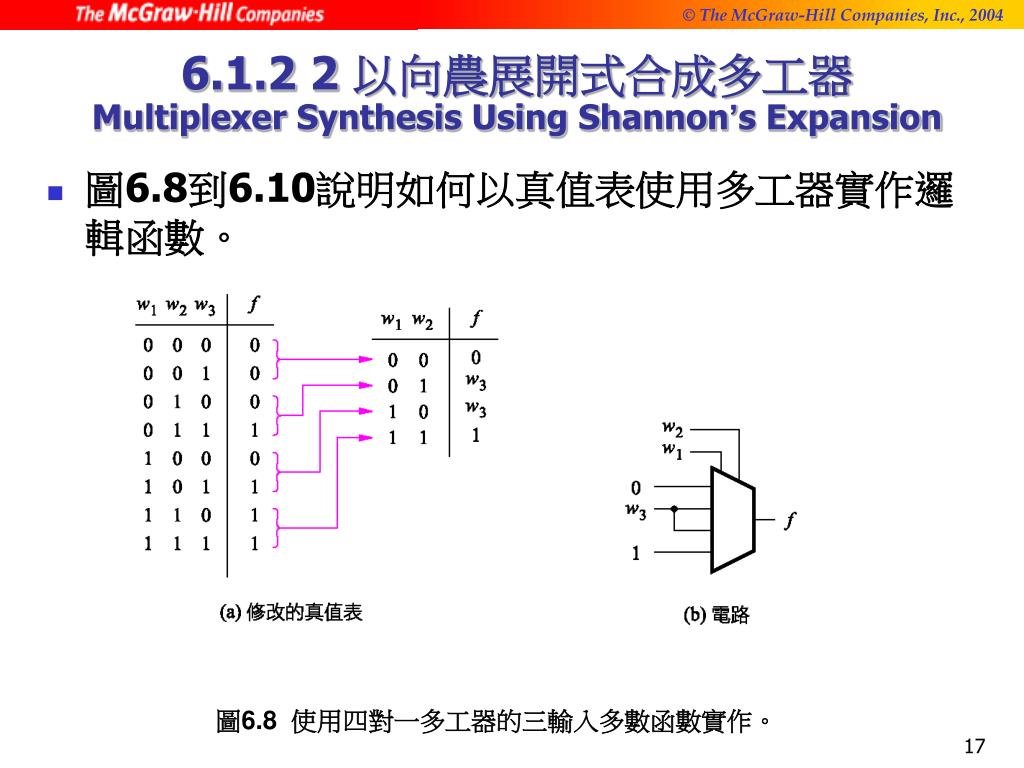

8对1多工器verilog-210 verilog语言编写8路分配器 2101 本节目录 1)本节目录; 2)FPGA简介; 3)verilog简介; 4)verilog语言编写8路分配器; 5)本节结束。 2102 FPGA简介 FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的, 也可以添加使能控制端对所接成的8选1数据选择器的工作状态进行控制。添加使能控制端的8选1数据选择器的电路如图5所示。 由图5可知,当=0时,8选1数据选择器正常工作;当=1时,8选1数据选择器的输出被锁定在低电平。 2)用多路选择器设计组合逻辑电路 由表2可知,具有两位地址输入a0、a1的4选1

Verilog 3 組合邏輯電路 作者 陳鍾誠

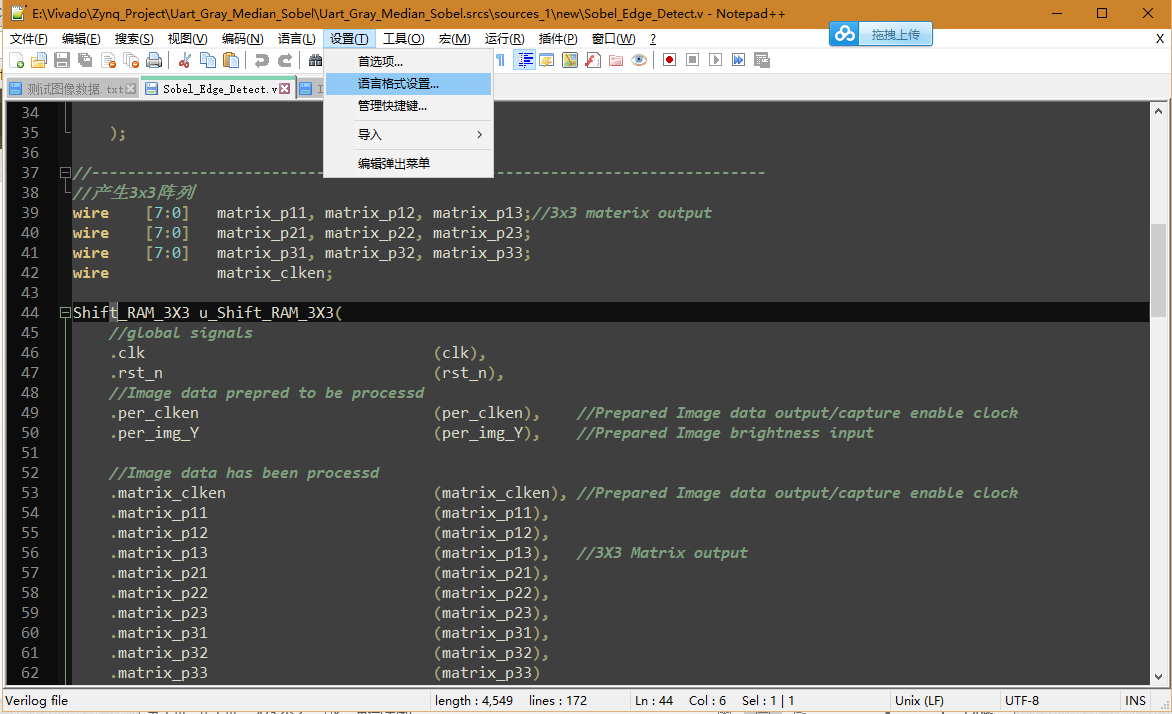

工欲善其事、必先利其器!要想高效的编写verilog没有一个好的编辑器可不行,所以我这里推荐两款十分好用的编辑器Notepad和Gvim,这两款编辑器由 NingHeChuan 零基础入门FPGA,如何学习? 问:本人零基础,想学FPGA,求有经验的人说说,我应该从哪入手,应该看什么教程,应该用什么学习板和开发计数器(1):Verilog常用写法 计数器是非常基本的使用,没有计数器就无法处理时序。我在学习时发现市面上有几种不同的计数器写法,非常有趣,在此记录下来: 一、时序逻辑和组合逻辑彻底分开 1代码 1 // ===== 2 // 名称 Count_1 3 // 作者 xianyu_FPGA 4 // 日期 5 // 描述 7445 ttl bcd—十进制代码转换/驱动器 ttl 161多路转接复用器多工器 ttl 双81多路转接复用器多工器 ttl 四41多路转接复用器多工器 7446 ttl bcd—7段低有效译码/驱动器 ttl 十位比较器 ttl 八进制计数器 ttl 三态同相2与使能端八总线缓冲器

图19 方法1的门级仿真波形 由图18和图19所示,虽然方法1加了 (* full_case *)修饰后,3选1多路选择器的综合结果没有产生锁存器,但是其功能仿真波形却当作锁存器来处理,而其门级仿真波形则是当作无关项来处理。 即方法1,其前后仿真结果是不一致的。 至于 基本的8對1多工器,使用Verilog與megafunction實現。 Introduction 使用環境:Quartus II 72 SP3 ModelSimAltera 61g DE2(Cyclone II EP2C35F672C6) Method 1: 自己撰寫Verilog mux_5_8_1v2v / Verilog 使用continuos assignment 我有很多麻烦,使这种问题的任何形式的感觉。我应该使用verilog为8位宽的2对1多路复用器创建一个模块。 问题: 编写使用8个赋值语句来描述电路的Verilog的模块。使用DE2板上的SW 17作为s输入,将7:0切换为X输入,将15:8切换为Y输入。将SW开关连接至红灯LEDR,并将M输出至绿灯LEDG 7:0。

用Verilog HDL设计2位16进制计数器 频道 我是一名拥有多年工 最新精品资料推荐提供全程指导服务 16 全新精品资料全新公文范文全程指导写作 –独家原创 11 57作经验的计生人,受党组织培养和教育多年,培养了我"服从命令听 从指挥"、 "能吃苦、能战斗、能奉献"的良好品 如图3所示,寄存器A的0~4 bit分别对应ADC通道CH0~CH4,5~7 bit保留;寄存器B的8 bit分别对应采样率FS0~FS7。如果要选择某几个通道,只需将寄存器A中相应的位置1,其他位置0,AD采样控制模块就会根据该寄存器中的内容使能相应的通道。如果要选择某一个采样频率,只需把寄存器B中相应的位置1,其他 Verilog学习(13)PLL与搜索代码 一:串行解串器的包格式与搜索代码 1:并行输入32bit数据,串行传输时,有特定的格式 上面的x表示8比特有效数据里的某一个比特。 先发送和接收的是MSB(左侧数据)。 为了给接收端的PLL提供一个同步的时钟,我们将在这个串行

Http Eportfolio Lib Ksu Edu Tw User 4 9 4970j014 Repository 100 1 Ksu Verilog 03 Lecture Pdf

解碼器 維基百科 自由的百科全書

基于Verilog实现电器定时开关控制 1146 预计 8 分钟读完 随着当今社会工作和生活节奏的加快,人们对许多电器、仪器、设备的自动化要求也越来越高,但现有的许多电器还不具备定时开启和关闭功能,许多需要在固定时间开关的装置,还需人工值守和 38译码器4选1多路选择器doc,专 业: 计算机科学与技术 班 级: 计实1001 学 号: U 姓 名: 王宸敏 电 话: 邮 件: @ 完成日期: 周一晚上 指导教师: 吴非 实验报告 一、实验 Verilog电路设计与仿真 二、实验目的 学习掌握用Verilog进行组合电路设计和时序逻辑电路设计 38译码器Verilog仿真与实现docx, PAGE \* MERGEFORMAT 6 思考题解答 思考题: Verilog HDL语言设计一个3线8线译码器。 要求:首先定义一个3 输入与门;然后以3 输入与门为基础设计一个3线8线译码器。 解答 步骤一 建立Quartus工程,作业中选择了与Altera公司提供的DE1开发板相对应的FPGA器件型号,如下图: 步骤二

Http Leiblog Wang Static Fpga Books E5 8f E5 Ae 87 E9 97 Verilog E7 8f E5 85 B8 E6 95 99 E7 A8 8b Pdf

转载 多工器mux Coding Style整理 Soc Verilog Quartus Ii 拥有梦想 与非博客 与非网

对与锁存器而言,锁存器在待处理信号存在Glitch的情况下,可能会对Glitch产生锁存,从而导致锁存出现严重错误,是目标信号处理结果与预期目的产生极大的偏差,因此锁存器存在不稳定因素,所以在使用锁存器时,要牢记优先消除待处理信号的Glitch。 本回答被网友采纳 已赞过 已踩过 你对多路复用器 1 含义 电子学中,多路复用器(multiplexer或mux)能从多个模拟或数字输入信号中选择某个信号并将其转发,将不同的被选信号输出到同一个输出线路中。 复用技术可能遵循以下原则之一,如:TDM、FDM、CDM或WDM。 复用技术也应用于软件操作上,如Problem 60 2to1 multiplexer (Mux2to1) 从本题开始的五道题将讨论数字电路中的多路选择器的使用。选择器是一个使用频次很高的模块,选择器从多个输入数据流中选取一个输出到公共的输出端。在综合的过程中一些 Verilog 语法会显式地被"翻译"为选择器,可以在综合

Verilog 延时10ns Verilog 传输延迟 数码管verilog延时程序

Fpga通过spi对adc配置简介 五 Verilog实现3线spi配置 小青菜哥哥的博客 程序员宅基地 程序员宅基地

38译码器,4选1多路选择器,Verilog HDL 文采飞扬才情过人李白唐伯虎杜甫泰戈尔在世看此文章必定甘败下风从此无脸见人,在下对 你的敬佩之意有如滔滔江水连绵不绝。 数组 存在重复元素 兴趣使然的程序猿 学习的道路上一起进步,也期待你的关注与支持! 您愿意向朋友推荐"博客详情 MUX 多工器 已赞过 已踩过 你对这个回答的评价是? 评论 收起 其他类似问题 DSP中的MUX是什么意思 14;71 Verilog 除法器设计 分类 Verilog 教程 除法器原理(定点) 和十进制除法类似,计算 27 除以 5 的过程如下所示: 除法运算过程如下: (1) 取被除数的高几位数据,位宽和除数相同(实例中是 3bit 数据)。 (2) 将被除数高位数据与除数作比较,如果前者不小于后者,则可得到对应位的商为 1,两者做差

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

Verilog上机实验 三 整数乘法器 码农家园

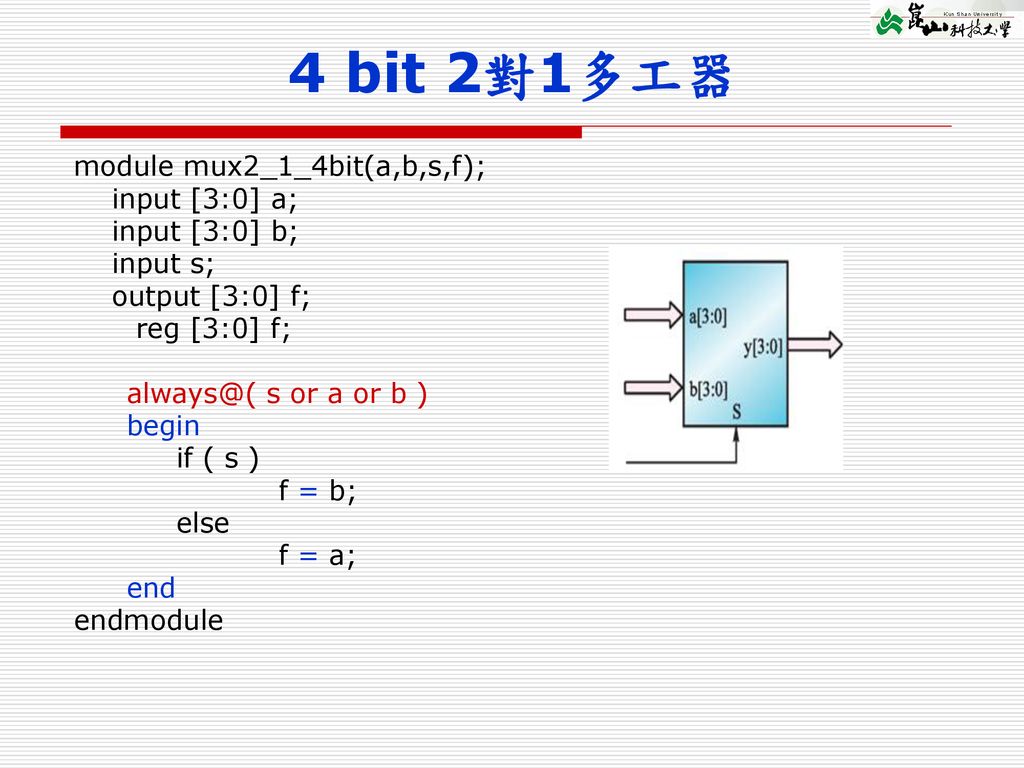

Verilog 学习过程 2选1多路选择器设计 12 Verilog 4位 二选一 多路选择器 hyhop150 收藏 19Verilog语法之三:变量 罗成 FPAG高级工程师 58 人 赞同了该文章 本文首发于微信公众号"花蚂蚁",想要学习FPGA及Verilog的同学可以关注一下。 变量即在程序运行过程中其值可以改变的量,在Verilog HDL中变量的数据类型有很多种,这里只对常用的几种进行介绍图 1 结构框图 Fig1 Structure diagram 2 序列检测器的基本工作过程(The basic working process serial detector) 有限状态机一般用来检测一组或多组由二进制码组成的脉冲序列信号,广泛应用于在数字 系统中。当该特定序列检测器连续接收到一组二进制码,如果这组二进制码与检测器中预先设 置的码

Verilog Pdf

大享 Verilog 硬體描述語言 第二版 全華 480 蝦皮購物

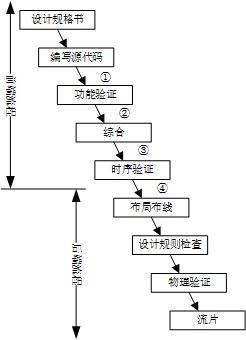

16 本章小结 通过对 EDA、HDL、FPGA、LCD1602 的了解使我们对篮球计分器的设计 有了更进一步的了解,是我们更加深入的了解篮球计分器设计所需用到的知识, 通过对设计流程和设计要求的描述,使我们对篮球计分器的设计有了一个总体框 架,为后续的具体设计做 序列检测器设计_modelsim_verilog_实验报告doc,实验四序列检测 一、实验目的: 1实验目的:通过学习硬件编程语言,掌握一般时序逻辑分析的方法。 2学会使用Verilog语言编写实现任意序列检测。 3学会使用Verilog编写测试文件testbech的方法并在Modelsim中实现时序仿真。虽然 EDA 工具可以对组合逻辑设计进行 重新优化组合,但在 Verilog 描述中使用括号可以降低 EDA 工具的压力,并且减少工 具的综合时间。 在下面的例子中,虽然 y2 和 y1 的功能是一样的,但 y1 会使用三级加法器,使用 括号的 y2 只使用二级加法器。 always @ (a1 or a2 or b1 or b2 or c1 or c2 or d1 or d2 begin y1 = a1 b1 c1

Verilog高级数字系统设计技术与实例分析 价格目录书评正版 中图网

Fpga通过spi对adc配置简介 五 Verilog实现3线spi配置 小青菜哥哥的博客 程序员宅基地 程序员宅基地

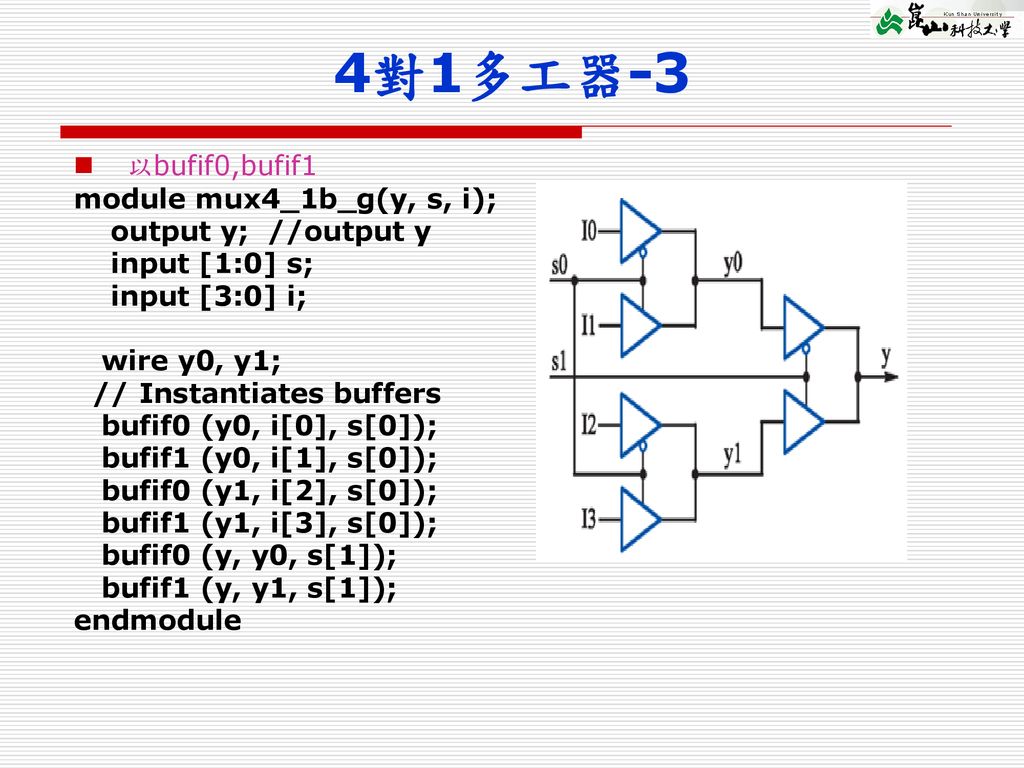

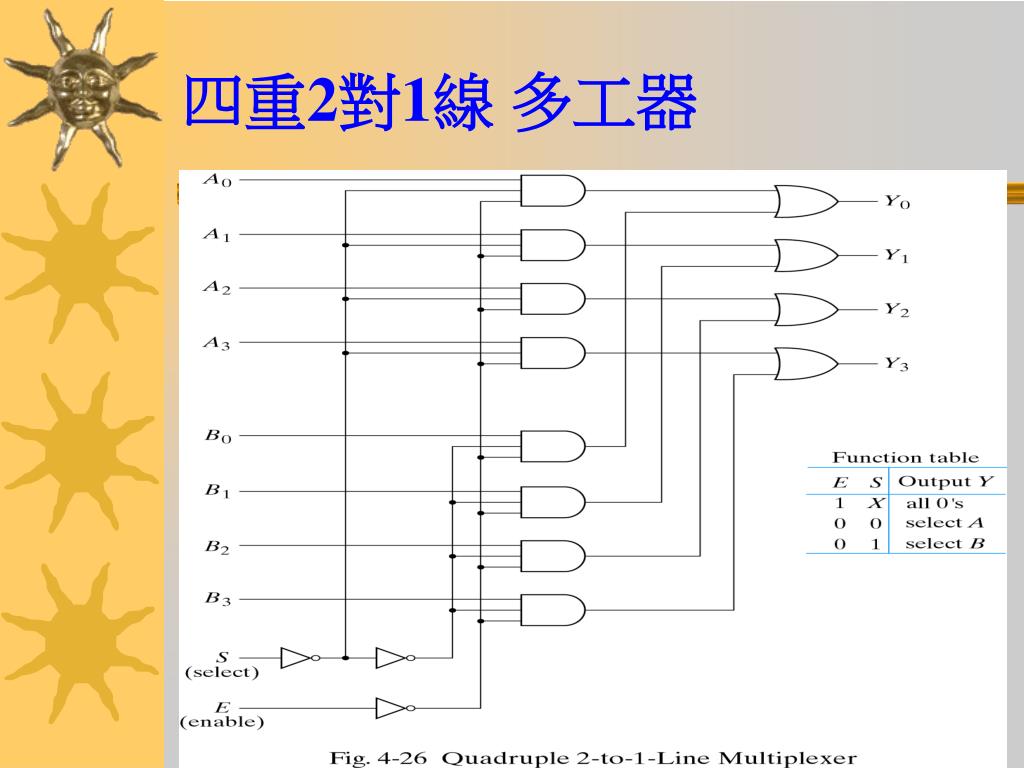

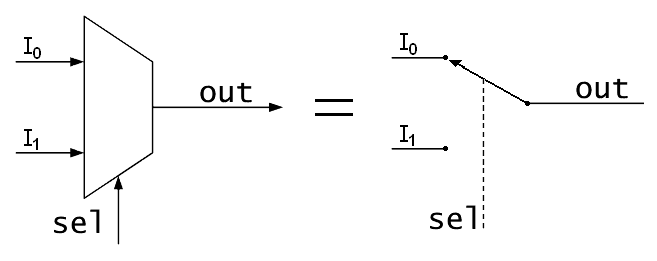

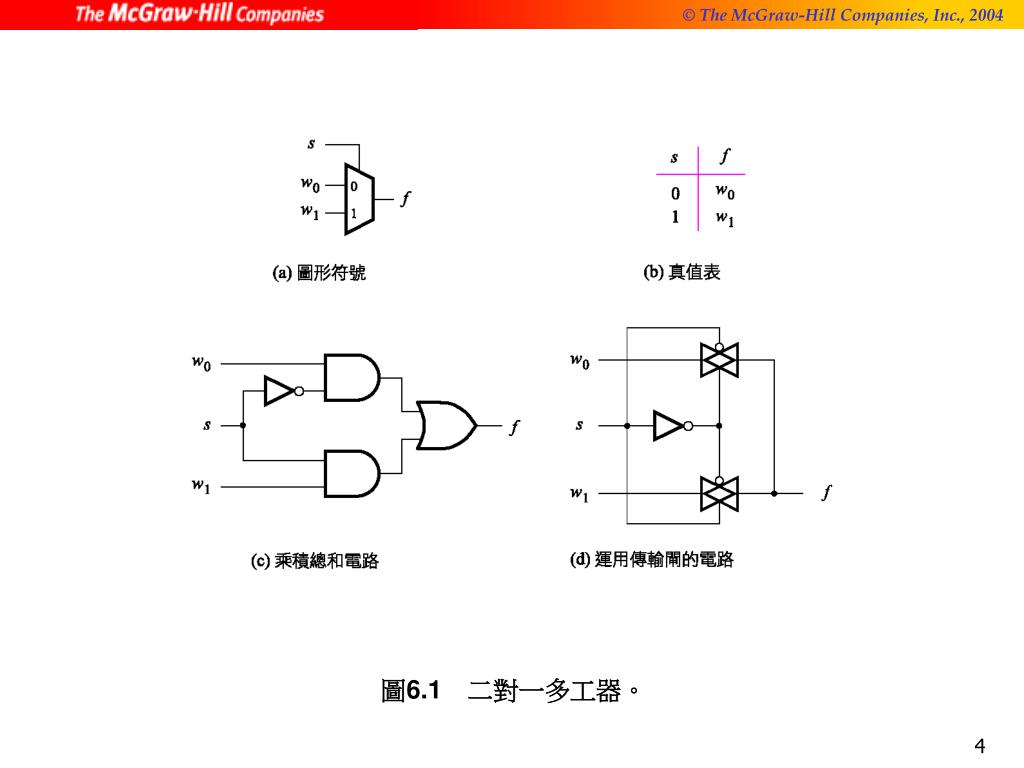

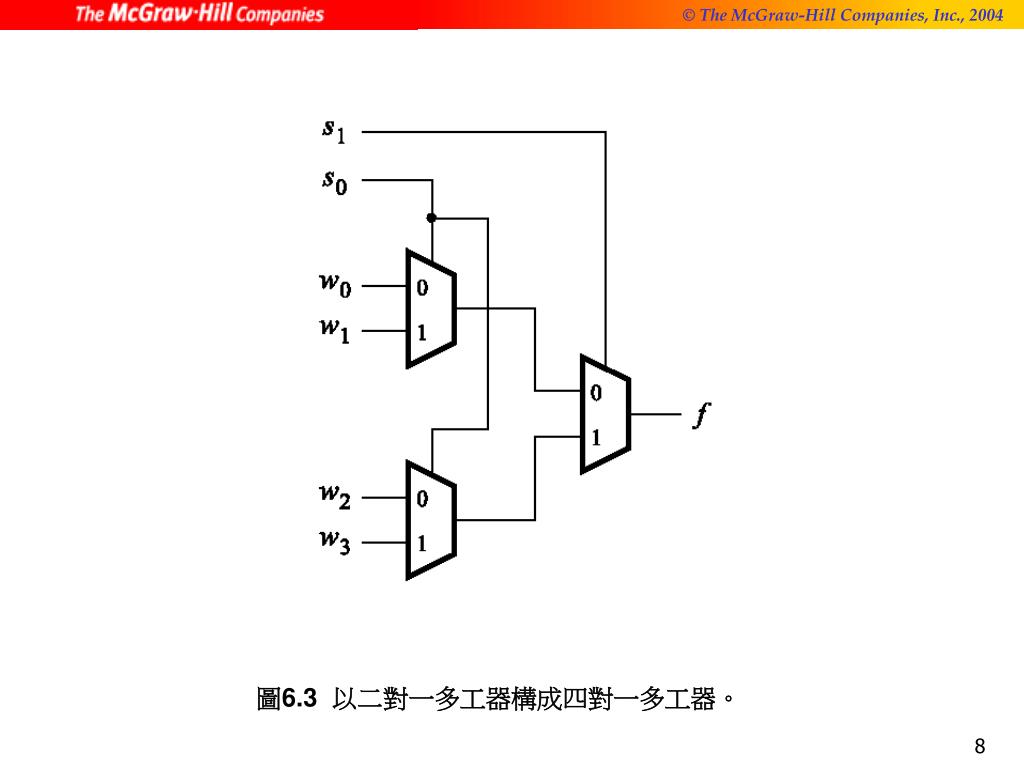

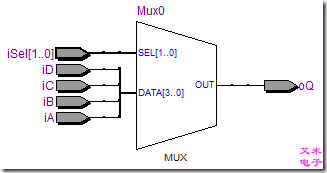

当移位信号到来时,移位寄存器就对存储的二进制进行移位操作移位寄存方式可自行设置(可 左移,右移,一位移,多位移位寄存)。移位寄存器需要将寄存器中的各位数据在移位控制信号的作用 下,依次向高位或是低位移动移位。 移位寄存器中的数据可以在移位脉冲 多工器 多工器(Multiplexer)缩写MUX;或称资料选 择器(Data Selector)功能图如下,它乃利用 资料选择线来选择资料输入线的其中一条,将 此条资料送至输出端Y 多工器 21 MUX 41 MUX 多工器 使用结构模型去描述 OK,but so tired Using dataflow! 题目描述通过使用ISE软件进行4位2选1多路选择器的设计与实现。题目解读这是一个很基本的Verilog语法,4位就是指输入的数是一个四位2进制的数,具体表达为4'b1000等等 Verilog4位2选1多路选择器 Lrrent 1033 收藏 10 分类专栏: Verilog 文章标签: Verilog 版权声明:本文为博主原创文章

數位邏輯設計與實習ch07 Verilog語法 Ppt Download

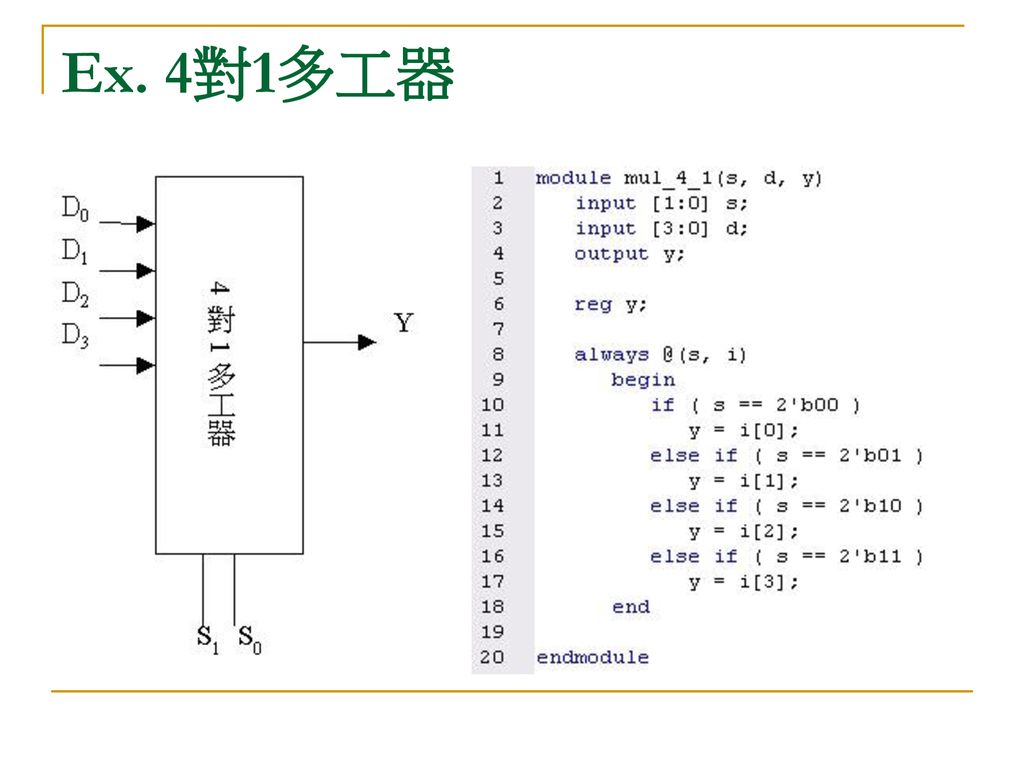

1 Chapter 12 Verilog 設計實際介紹邏輯層次的設計實際介紹資料流層次的設計實際介紹行為層次的設計實際介紹 Ppt Download

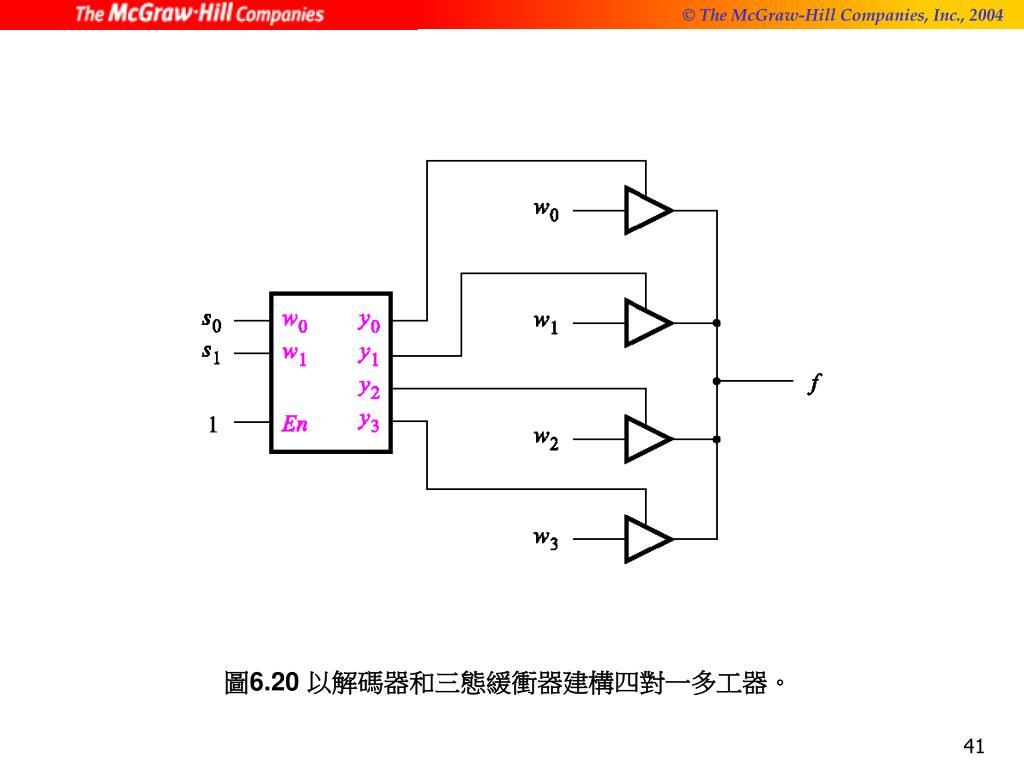

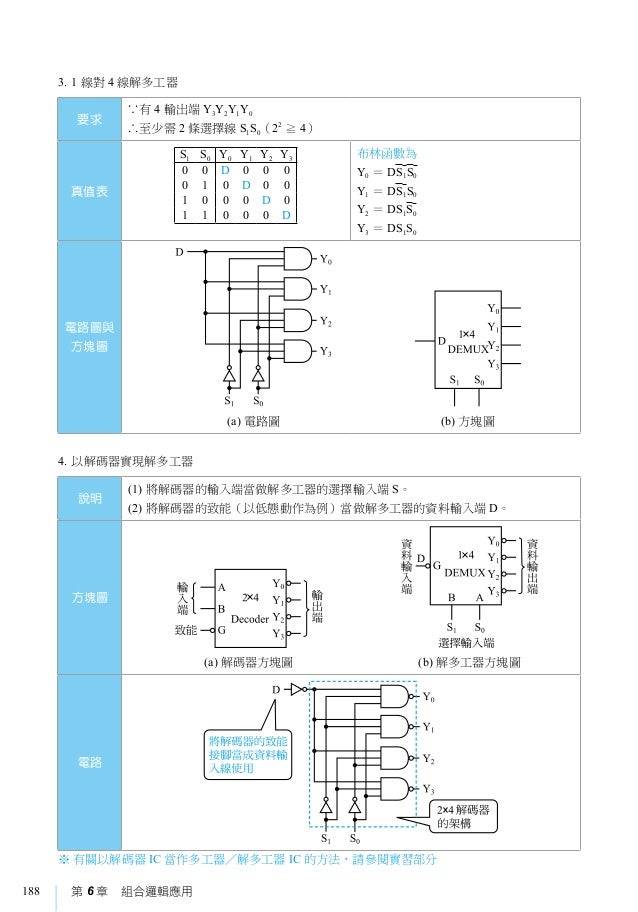

解多工器(demultipexer,DeMUX) 比較器(comparator) 解碼器 是電子技術中的一種多輸入多輸出的組合邏輯電路,負責將二進制代碼翻譯為特 定的物件(如邏輯電平等),功能與編碼器相反。解碼器一般分為通用解碼器和數位顯示解碼器兩大類。 2选1多路选择器的Verilog hdl 可选中1个或多个下面的关键词,搜索相关资料。 也可直接点"搜索资料"搜索整个问题。 #热议# 开放三孩政策你怎么看? 其中a为输出,s为选择信号,x和y分别为被选择的信号。 s为0时,输出y信号;s为1时,输出x信号。 这几个 本文整理出幾種常見的多工器mux可合成的coding style,並深入探討其合成的結果。 Introduction 使用環境:NCVerilog 54 Debussy 54 v9 Quartus II 81 (同一種coding style在不同synthesizer下會有不同的認知,甚至相同synthesizer不同版本也會不同,本文僅討論Quartus II 81下的實驗結果)。 各種coding style的RTL Viewer比較 1

转载 多工器mux Coding Style整理 Soc Verilog Quartus Ii 拥有梦想 与非博客 与非网

Http D1 Amobbs Com s Upload7111 Files 46 Ourdev 6052gw97xl Pdf

针 对 Wallace树 型 乘 法 器 的 Verilog源 代 码 设 计 提 出 改 进 ,设 计 了 一 个 自 动 生 成 Verilog x x x x x x 代 码 的 应 用 程 序 ,可 自 动 生 成 8 8 、24 2 4 、24 2 6 、24 2 8 、26 2 4 和 26 2 6 位 Wallace树 型 乘 法 器 ,采 用 仿 真 软 件 对 生 成 的 Verilog代 码 进 行 了 测 试 ,解 决 了 人 工 输 入 Verilog verilog语言编写八选一数据选择器docx,Verilog——八选一选择器 PAGE 1 八选一选择器 实验目的 编写一个八选一的选择器,并在verilog软件上进行仿真。 代码 源代码 (1)用数据流描述的八选一多路选择器模块,采用了逻辑方程 module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0);图8 :8个位宽1多路选择器构成位宽8的多路选择器 这种设计方法,不在提供设计源码,读者可以自行讨论设计。 第二种方法,根据verilog的设计规则,可以直接描述逻辑功能,而不用描述门电路。

Ppt 數位邏輯 使用verilog 設計powerpoint Presentation Free Download Id

博客來 Verilog 晶片設計 附範例程式光碟 第三版

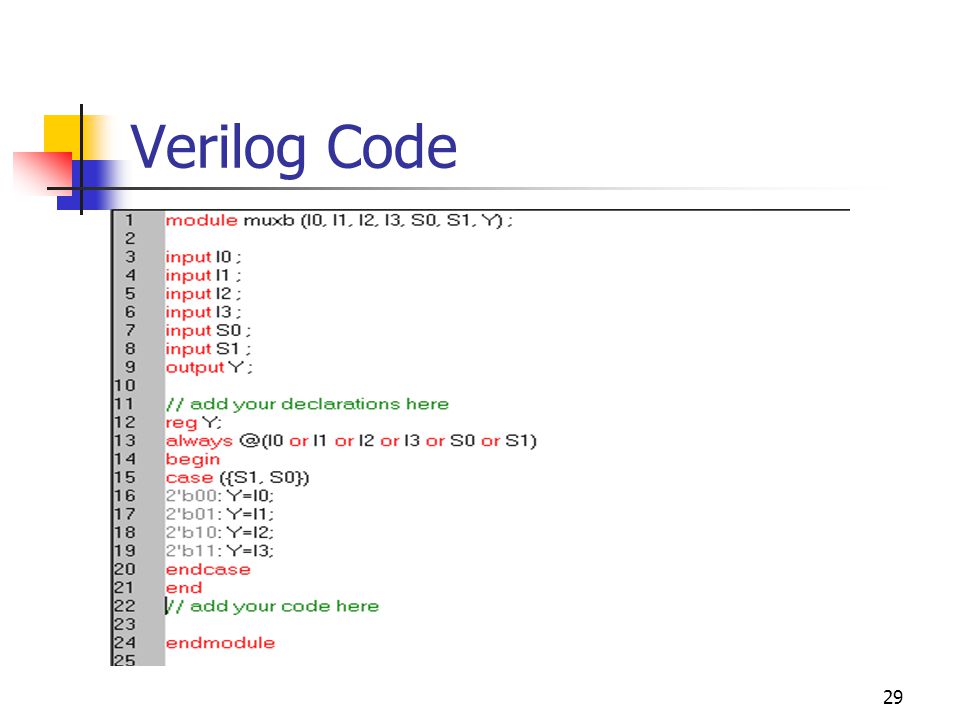

对读者的假设已经掌握:可编程逻辑基础 Verilog HDL基础 使用Verilog设计的Quartus II入门指南 使用Verilog设计的ModelSIm入门指南 内容1 多路选择器Multiplexer此处所说的多路选择器,为组合逻辑电路中的多路多路选择器:多路输入,一路输出。 11 不带优先级的多路选择器111 使用case语句描述此处以

F 10 11 老師示範2位元2對1多工器

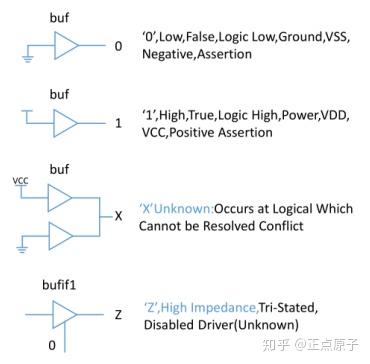

正点原子fpga连载 Verilog Hdl语法 摘自 正点原子 开拓者fpga 开发指南 知乎

从仿真器的角度理解verilog语言 知乎

105 年 數位電子乙級工作項目06 邏輯設計 阿摩線上測驗

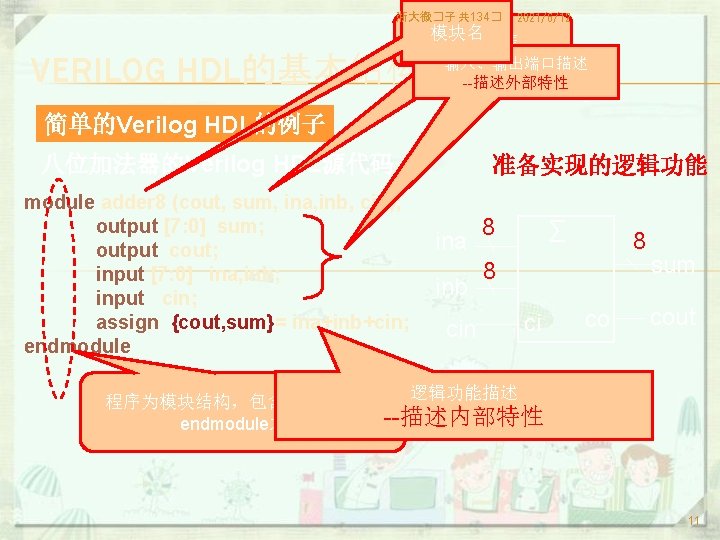

134 Verilog Hdl Verilog Hdl Verilog Hdl

Http Www Cs Thu Edu Tw Upload Files 99 Liaw 01 Pdf

Ppt 第四章powerpoint Presentation Free Download Id

Http Eportfolio Lib Ksu Edu Tw User T H 4990k059 Pdf

数据选择器 维基百科 自由的百科全书

Http Leiblog Wang Static Fpga Books Verilog E9 A3 E4 Ba 9b E4 Ba 8b E5 84 Bf 03verilog Hdl E9 A3 E4 Ba 9b E4 Ba 8b E5 84 Bf E6 97 B6 E5 Ba 8f E7 Af 87v2 Pdf

Verilog入門教學 本篇 1 Verilog基礎語法 哔哩哔哩 つロ干杯 Bilibili

Verilog 3 組合邏輯電路 作者 陳鍾誠

Verilog Fpga 晶片設計 附光碟 九成新 蝦皮購物

大享 數位邏輯設計 第六版 精裝本 全華 露天拍賣

Www Cyut Edu Tw Yfahuang Chap04 Pdf

史丹利部落格 多工器4對1

Clementyan 筆記分享 Verilog Fpga Homework 多工器

Verilog Chap4 4 11 U7d44 U5408 U96fb U8def U7684 U786c U9ad4 U63cf U8ff0 U8a9e U8a00 O U9598 U968e U5c64 U6a21 U578b U95dc U9375 U5b57 And U3001nand U3001or U3001nor U3001xor U3001xnor U3001not U3001 Buf Hdl U7bc4 U4f8b Course Hero

Fpga数字信号处理 十七 多级cic滤波器verilog设计 Fpgadesigner的博客 程序员宅基地 程序员宅基地

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Www Cyut Edu Tw Yfahuang Chap04 Pdf

Verilog之ps2协议 U的专栏 程序员宅基地 程序员宅基地

Ch01 2 Verilog語法資料流 Dataflow 設計行為 Behavior 設計 Ppt Download

Verilog Chap4 4 11 U7d44 U5408 U96fb U8def U7684 U786c U9ad4 U63cf U8ff0 U8a9e U8a00 O U9598 U968e U5c64 U6a21 U578b U95dc U9375 U5b57 And U3001nand U3001or U3001nor U3001xor U3001xnor U3001not U3001 Buf Hdl U7bc4 U4f8b Course Hero

Ppt 數位邏輯 使用verilog 設計powerpoint Presentation Free Download Id

Verilog 3 組合邏輯電路 作者 陳鍾誠

掌握 數位邏輯 含實習 複習講義電子試閱本

Http Www Scirp Org Journal Paperdownload Aspx Paperid Type Epub

1 Chapter 12 Verilog 設計實際介紹邏輯層次的設計實際介紹資料流層次的設計實際介紹行為層次的設計實際介紹 Ppt Download

Cycu Ee Computer Networks Systems Research Lab Hdl Study Group Ppt Download

Www Cyut Edu Tw Yfahuang Chap04 Pdf

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

Www Cyut Edu Tw Yfahuang Chap04 Pdf

掌握 數位邏輯 含實習 複習講義電子試閱本

转载 多工器mux Coding Style整理 Soc Verilog Quartus Ii 拥有梦想 与非博客 与非网

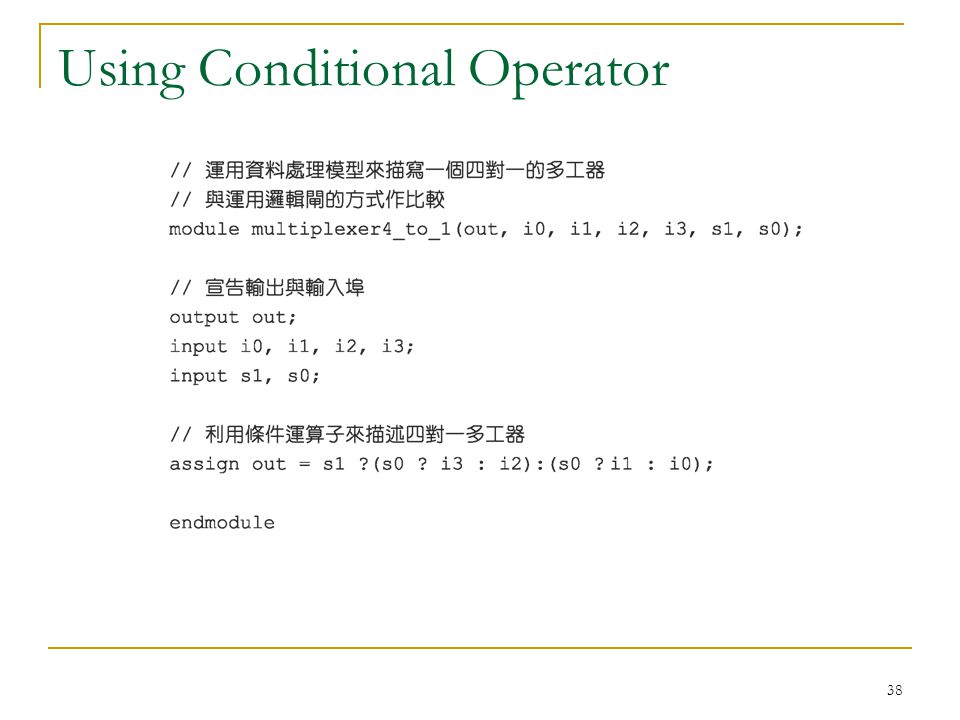

Chap 6 Dataflow Modeling Ppt Download

Ppt 數位邏輯 使用verilog 設計powerpoint Presentation Free Download Id

Verilog Hdl数字设计与综合 第二版 本科教学版 Samir Palnitkar S 帕尔尼卡 著 高清pdf电子书下载 颜回书舍

數據多工器 維基百科 自由的百科全書

5 语法篇 Verilog Hdl基础语法 1 哔哩哔哩 つロ干杯 Bilibili

Verilog 3 組合邏輯電路 作者 陳鍾誠

Caslab Ee Ncku Edu Tw Dokuwiki Media Course Ldl 108b Laboratory 8 Pdf

博客來 數位邏輯設計與晶片實務 Verilog 附範例程式光碟 第三版

大享 Fpga系統設計實務入門 使用verilog Quartus版 全華 蝦皮購物

數位邏輯設計 使用verilog Hdl 三民網路書店

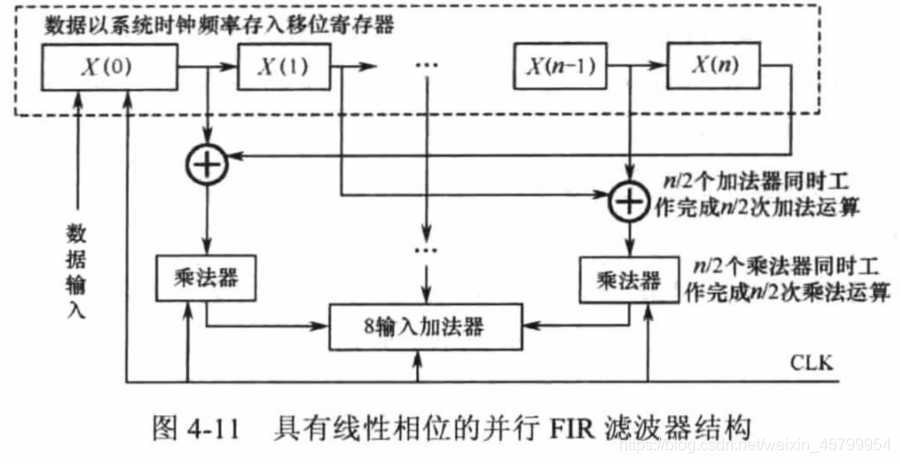

Verilog并行fir滤波器设计 千万小心的博客 程序员宅基地 程序员宅基地

Http Leiblog Wang Static Fpga Books Verilog E9 A3 E4 Ba 9b E4 Ba 8b E5 84 Bf 03verilog Hdl E9 A3 E4 Ba 9b E4 Ba 8b E5 84 Bf E6 97 B6 E5 Ba 8f E7 Af 87v2 Pdf

Ppt 數位邏輯 使用verilog 設計powerpoint Presentation Free Download Id

2 1 Verilog 3 8 译码器 Hyhop150的专栏 Csdn博客

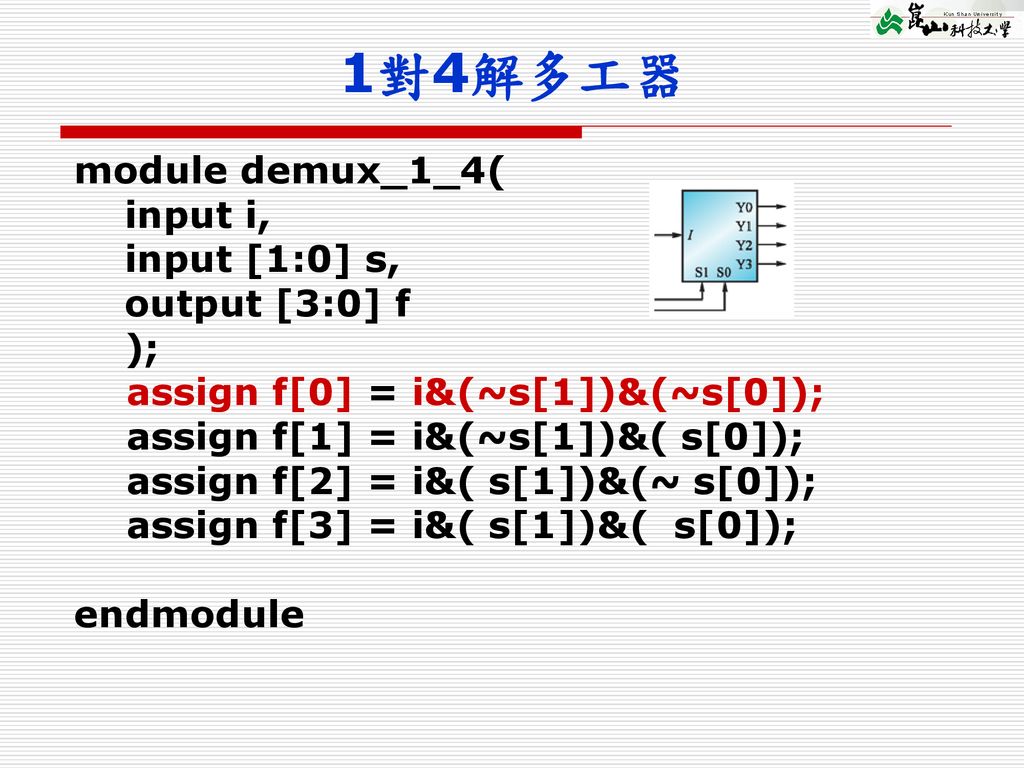

Alex9ufo 聰明人求知心切 數位ic設計入門 Verilog Combinational Logic 1 To 8 Demultiplexer 解多工器behavioral Modeling Test Bench

原創 哪一個計數器才會出現9呢 Soc Verilog 真oo无双 博客园

Verilog 3 組合邏輯電路 作者 陳鍾誠

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

Verilog 3 組合邏輯電路 作者 陳鍾誠

筆記 如何設計5位元的8對1多工器 Soc Verilog Megacore 学步园

Alex9ufo 聰明人求知心切 Verilog Demux 1 X 4 1對4解多工器資料分配器

Verilog Chap4 4 11 U7d44 U5408 U96fb U8def U7684 U786c U9ad4 U63cf U8ff0 U8a9e U8a00 O U9598 U968e U5c64 U6a21 U578b U95dc U9375 U5b57 And U3001nand U3001or U3001nor U3001xor U3001xnor U3001not U3001 Buf Hdl U7bc4 U4f8b Course Hero

Hdlbits Verilog学习笔记 Verilog Language Modules Hierarchy 哔哩哔哩

134 Verilog Hdl Verilog Hdl Verilog Hdl

Ch01 2 Verilog語法資料流 Dataflow 設計行為 Behavior 設計 Ppt Download

Verilog 的電路合成研究 以mux 多工器為例 使用altera Quartus Ii Rtl Viewer 檢視 Youtube

數位邏輯設計與實習ch07 Verilog語法 Ppt Download

浅谈verilog Hdl代码编写风格 知乎

Fpga系統設計實務 蕭宇宏 U05 組合邏輯電路實作 Ii 1 多工器實作 Youtube

Verilog传奇 从电路出发的hdl代码设计 吴涛 缪康 电子书下载 在线阅读 内容简介 评论 京东电子书频道

Alex9ufo 聰明人求知心切 數位ic設計入門 Verilog Combinational Logic 1 To 8 Demultiplexer 解多工器behavioral Modeling Test Bench

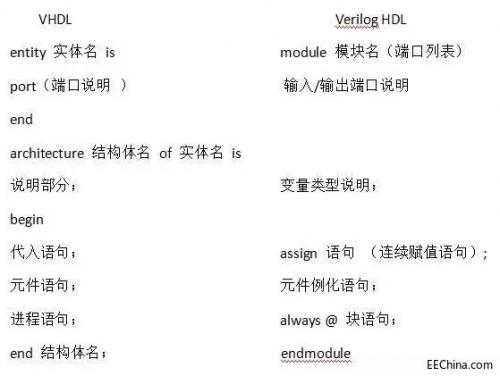

一文看懂vhdl和verilog有何不同 可编程逻辑 与非网

Caslab Ee Ncku Edu Tw Dokuwiki Media Course Ldl 108b Laboratory 8 Pdf

Verilog实现spi通信 包括对任务和函数用法的讲解 灰太狼的小秘密 Csdn博客

Ppt 數位邏輯 使用verilog 設計powerpoint Presentation Free Download Id

數據多工器 Wikiwand

二手書 9成新以上 七折 精裝 數位邏輯設計第6版使用verilog Hdl 林銘波全華 蝦皮購物

134 Verilog Hdl Verilog Hdl Verilog Hdl

文档 艾米电子 多路选择器与多路分解器 Verilog 安德鲁 博客园

Verilog语言培训 学习视频教程 腾讯课堂

少年科技人雜誌 15年6月號 Nand2tetris第1週 布林函數

Verilog入門教學 本篇 1 Verilog基礎語法 哔哩哔哩 つロ干杯 Bilibili

數據多工器 Wikiwand

基于fpga的洗衣机控制器verilog Hdl 语言描述的设计与开发 Doc下载

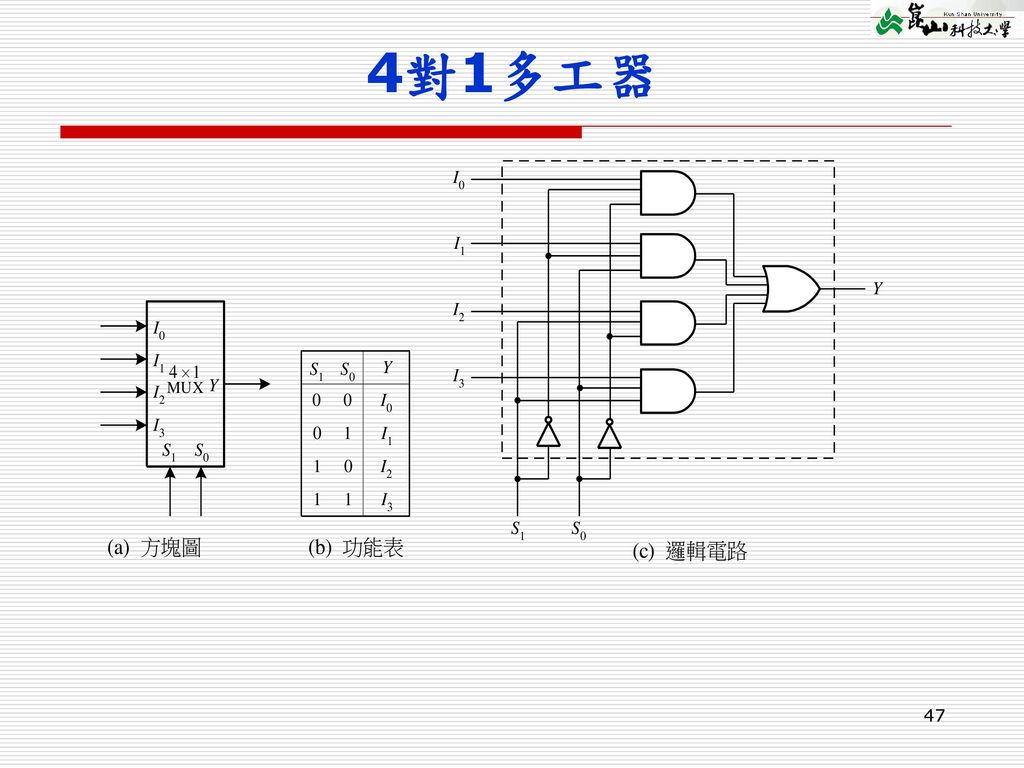

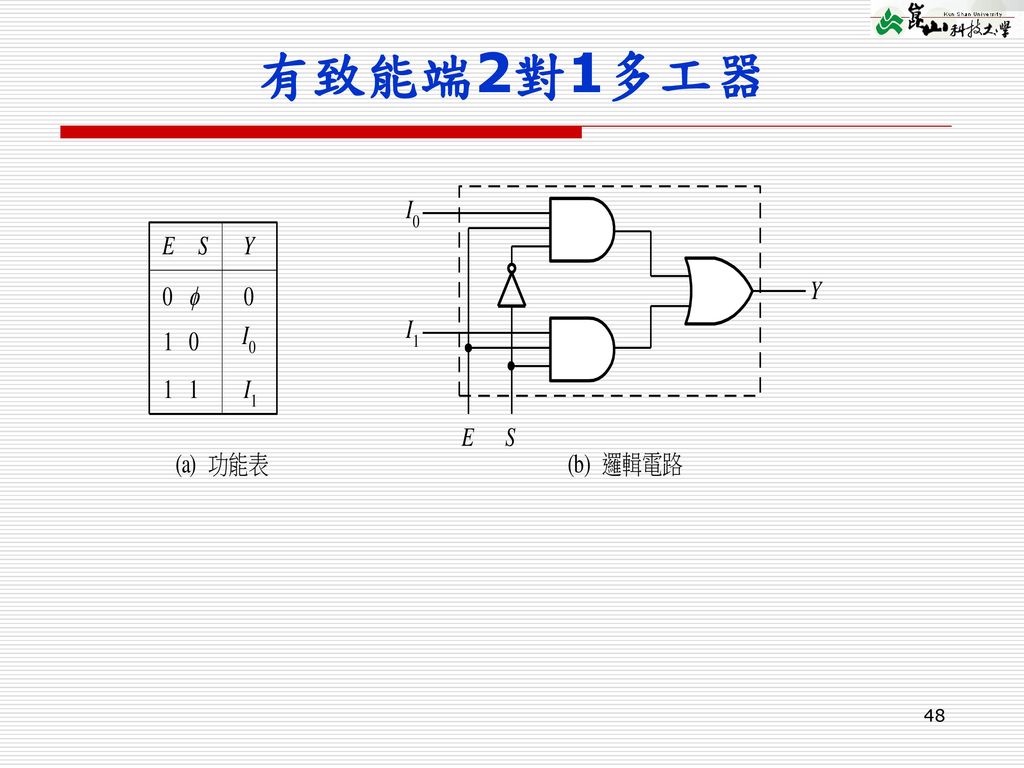

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

史丹利部落格 多工器4對1

コメント

コメントを投稿